Our research, in practice

Technologies

Demonstrating our Research

Our technologies demonstrate our research findings, through the fabrication of experimental test chips and the release of downloadable software tools.

Chip Demonstrators

Our test chips allow researchers to practically validate new designs and approaches, and are a central part of the Centre’s activities.

COILS-C1

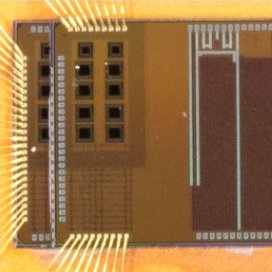

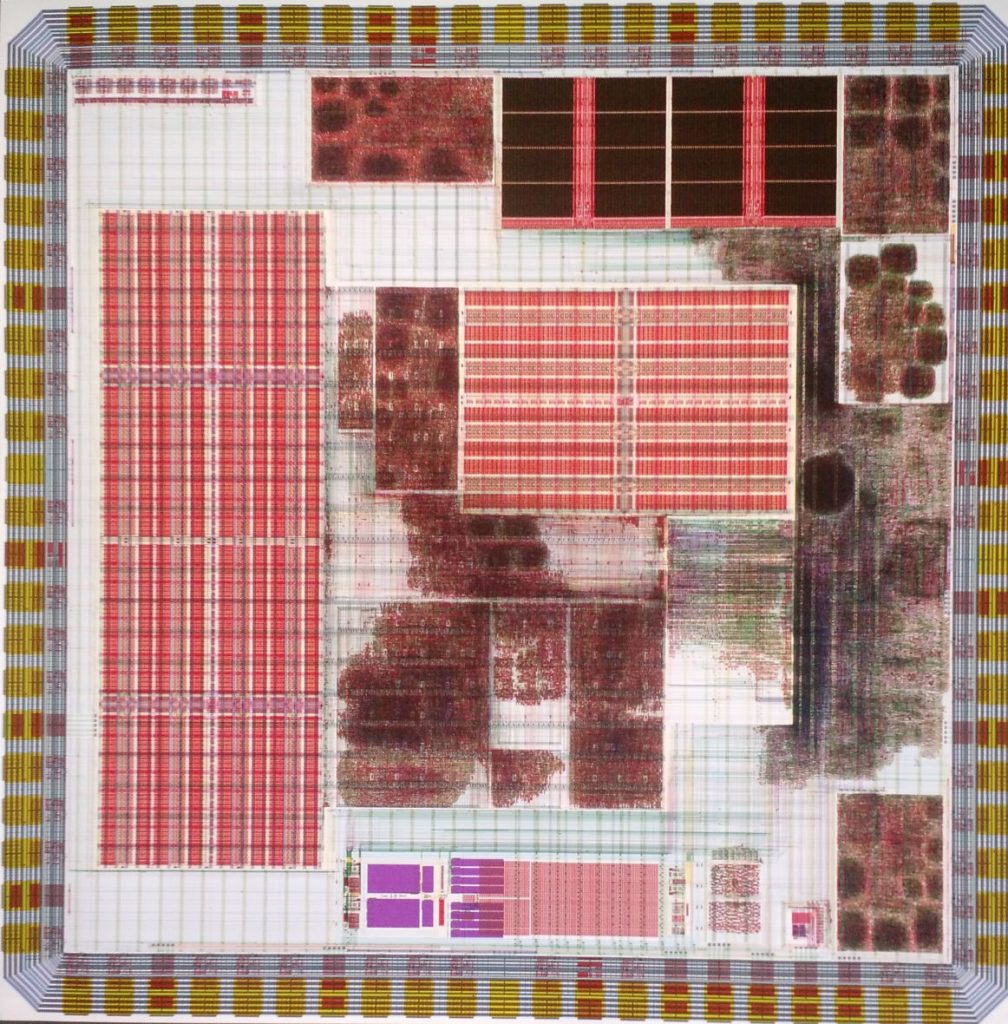

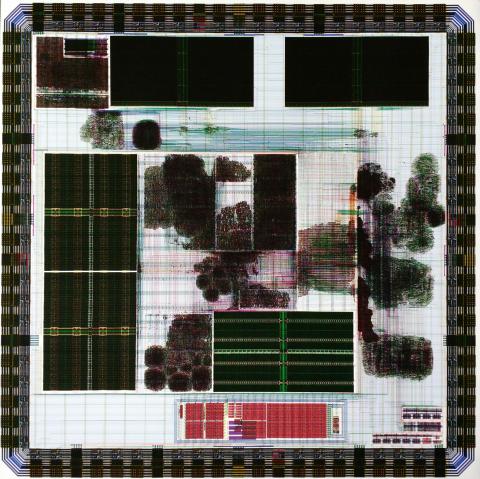

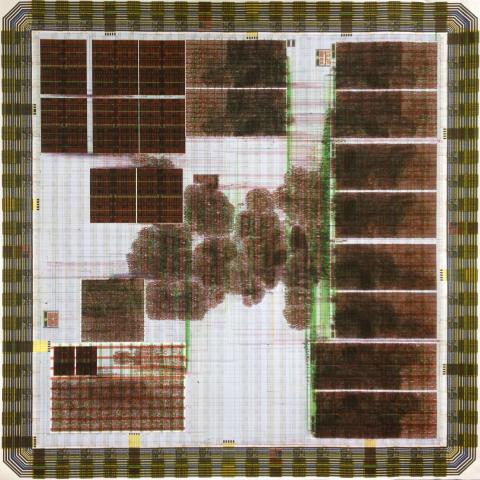

COILS-C1, taped-out out in November 2018, is the latest in a series of test-chips investigating low-cost 3D die stacking using near-field wireless communication. This two-tier SoC, fabricated using a TSMC 65nm process, incorporates two Arm Cortex M0 CPU cores in addition to a wireless vertical AHB lite bus for inter-layer power and data transfer. The wireless AHB-Lite bus consists of four, 250um diameter, inductive channels to simultaneously transmit data (at speeds up to 6Gbps) and wirelessly transfer power, whilst also allowing ‘plug-and-play’ integration with existing SoC AHB-Lite peripherals. Figure 1 – Illustration showing the key components of the COILS-C1 chip.

Read Article +

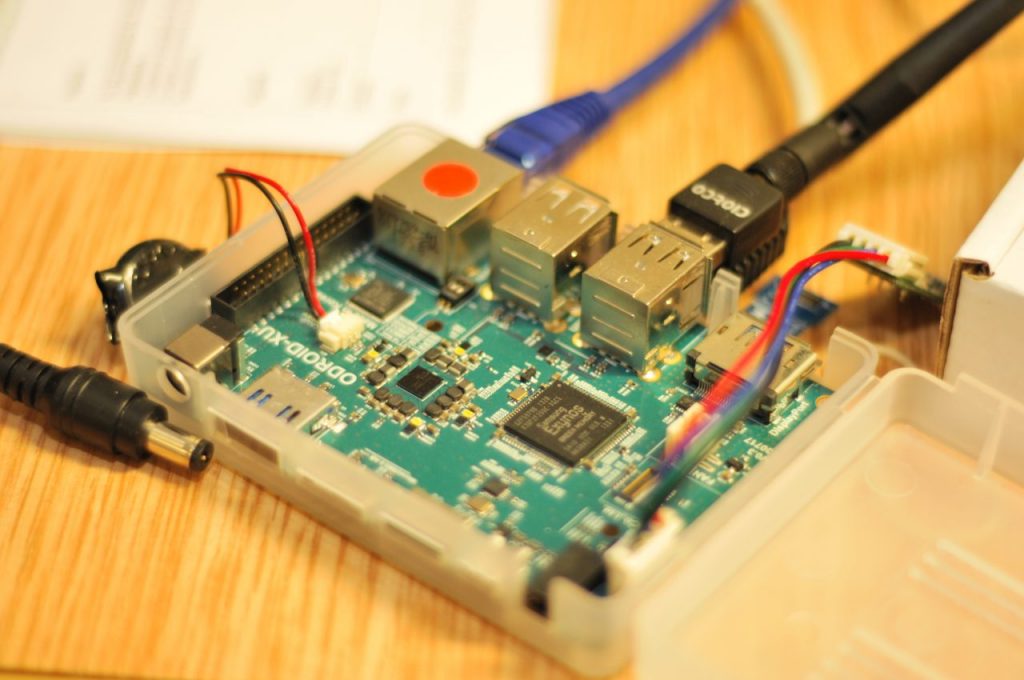

ICLexperimenter-2018

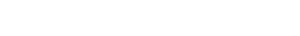

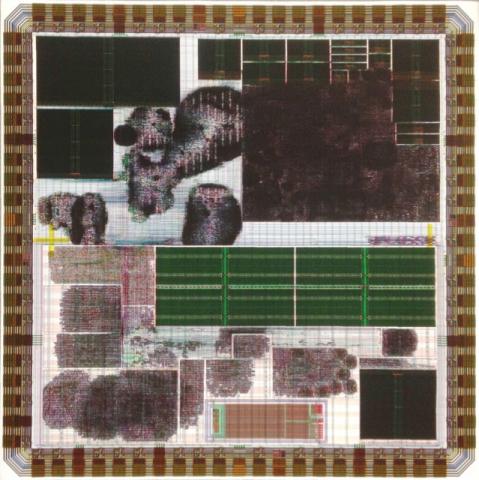

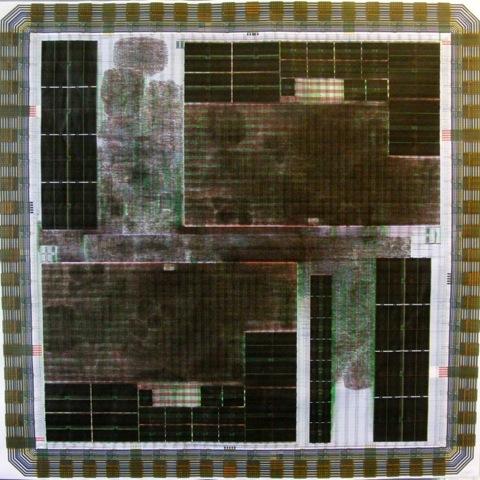

Taped-out in May 2018, ICL-Experimenter is the first in a series of Arm-ECS research centre test-chips designed to explore wireless 3D integration using inductive coupling links. The chip was fabricated in AMS 0.35um technology with two vertically stacked dies within each IC. This initial prototype contains eight wireless channels, each of which communicates over a distance of 120um (through 100um of silicon substrate + 20um of epoxy adhesive) and focusses on exploring different transceiver designs and inductor layouts. Wireless 3D integration is a novel approach to 3D die stacking which avoids the inflated design, fabrication and manufacturing costs associated with…

Read Article +

Pipistrelle-4

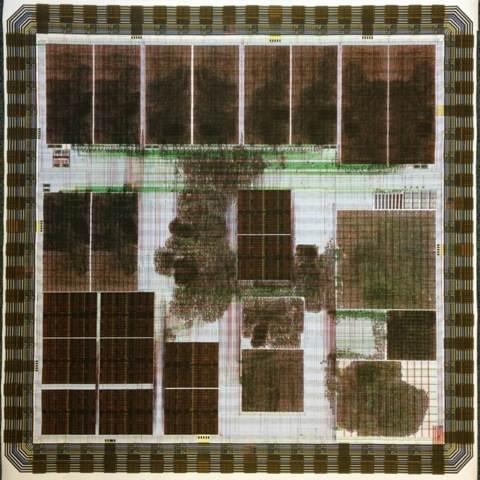

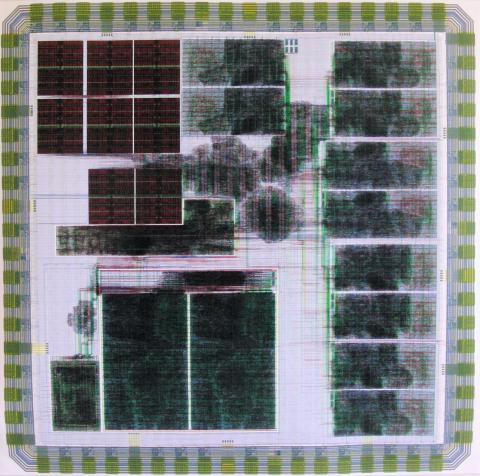

Pipistrelle-4, taped-out at the end of May 2017, is the latest in a series of low-energy sensor-system chips. The chip includes circuit/system ideas from multiple PhD research students and industry, focusing on an energy and performance optimised SRAM bitcell, low-area overhead energy-efficient flip-flops and standard-cells. The chip was taped-out during Yunpeng Cai’s internship at Arm Cambridge, and includes circuits to validate his novel flip-flop design which has now been patented. The prototype chips were received at the end of September 2017, and tested successfully.

Read Article +

ECStest-2016

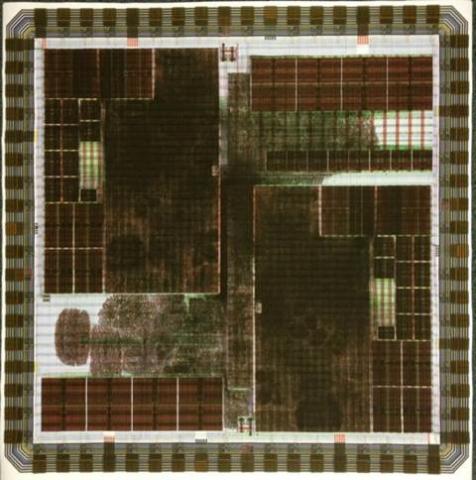

Taped-out in October 2016 this test-chip was designed to explore on chip wireless communication in the mm-wave frequency band. The chip was fabricated in an AMS 0.35um technology and incorporates two meander monopole antennas (which can be observed in the lower left and right corners of the die in Figure 1, see below), in addition to a range of other digital circuits. ECStest2016 Test Chip The chip was returned in May 2017 and has undergone rigorous testing for use in wireless on-chip clock distribution. a die photo of the fabricated antenna in addition to its performance. As can be observed…

Read Article +

Pipistrelle-3

Taped out in March 2016, this chip advanced Pipistrelle-2’s design by adding forward body-bias to improve performance at low voltage as well as an autonomous dynamic voltage and frequency scaling (DVFS) control state machine for carefully sequencing clocks, regulator settings and body-bias. Additional integration of the switched-capacitor regulator and harvester has been made possible by adding numerous low–power oscillators along with further efficiency improvement and a reverse current protection scheme.

Read Article +

Pipistrelle-2

This chip advances Pipistrelle-1’s design, taking another step towards filling in the pieces required to build an autonomous minimum-energy sensor system. Low power clock sources are an important part of a minimum energy system for driving CPUs, switched-capacitor converters, power-management unit logic, wake-up timers and more. This chip takes the first step to prototyping suitable fully-integrated oscillator topologies, as well as improving on previous versions of SRAM, power and energy harvesting converters. Pipstrelle 2 Test Chip

Read Article +

Pipistrelle-1

A sub-threshold demonstrator chip, incorporating innovative features for energy harvesting and power conversion, has been designed and taped-out by Arm R&D engineers and ECS researchers. Pipistrelle-1 Minimum energy systems are important for deployable multi-billion wireless sensor networks (WSNs). This sub-threshold chip, code-name “PIPISTRELLE-1”, was designed in the TSMC 65LP process. It demonstrates power conversion and energy harvesting techniques which are critical features for realising WSN SoCs, and serves as a platform for experimenting with various energy and power management algorithms and techniques.

Read Article +

Cricket-1

This demonstrator, code-name “Cricket-1”, was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Cricket-1 was taped out in September 2013, arriving back from fab in January 2014. It supports evaluation of area and power reduction techniques for IP watermarking. Cricket-1 IP watermarking demonstrator, TSMC65LP

Read Article +

Tokachi-4M

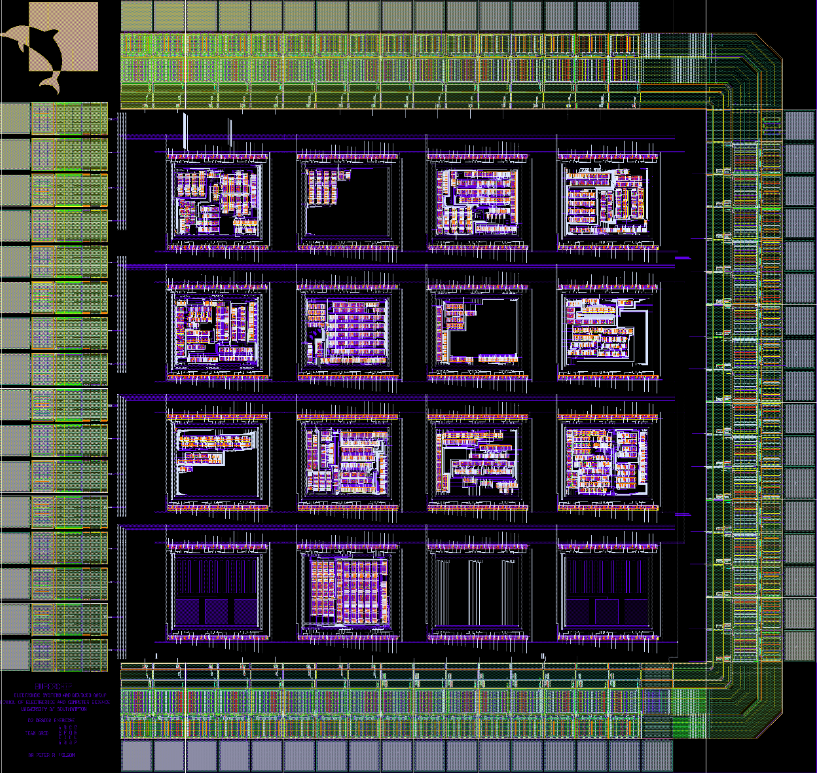

This low-power technology demonstrator, code-name “Tokachi-4M”, contains 16x Cortex-M0 CPU cores and was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Tokachi-4M was taped out in October 2012 and up and running on the bench late January 2013, and includes sub-threshold voltage experimental circuits and an IP watermarking characterization block. Tokachi-4M Tokachi-4M

Read Article +

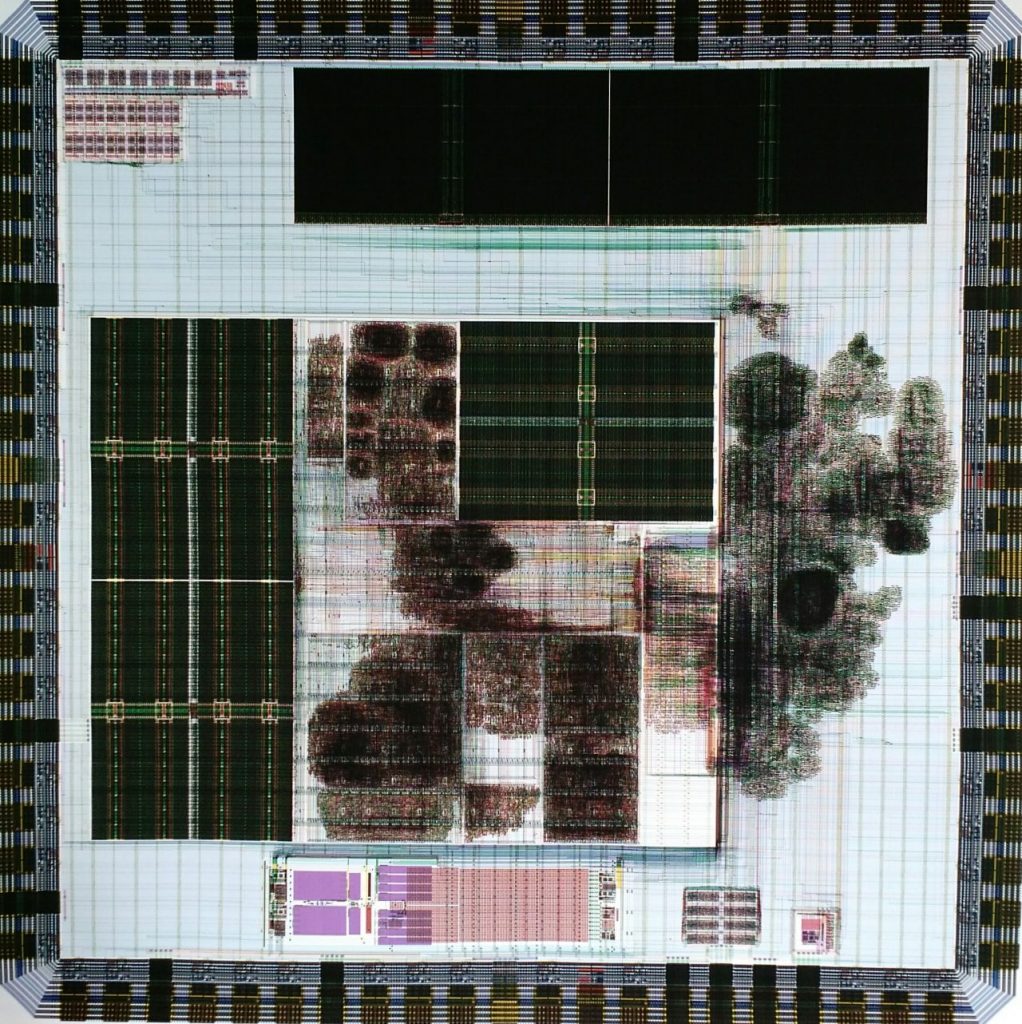

Tokachi-4A

This advanced state-retention power-gating demonstrator, code-name “Tokachi-4A”, contains a Cortex-M0 system control processor and a dual-core Cortex-A5 application processor subsystem, again designed as a collaboration with Arm Ltd on TSMC 65nm Low-Power process technology available. Tokachi-4A was taped out in October 2012 and working and in characterization at the end of January 2013, and the silicon includes an alternative implementation of the IP watermarking research circuitry. Tokachi-4A

Read Article +

Tokachi-3M

This demonstrator, code-name “Tokachi-3M”, was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Tokachi-3M was taped out in March 2012. Tokachi-3M IP watermarking demonstrator, TSMC65LP

Read Article +

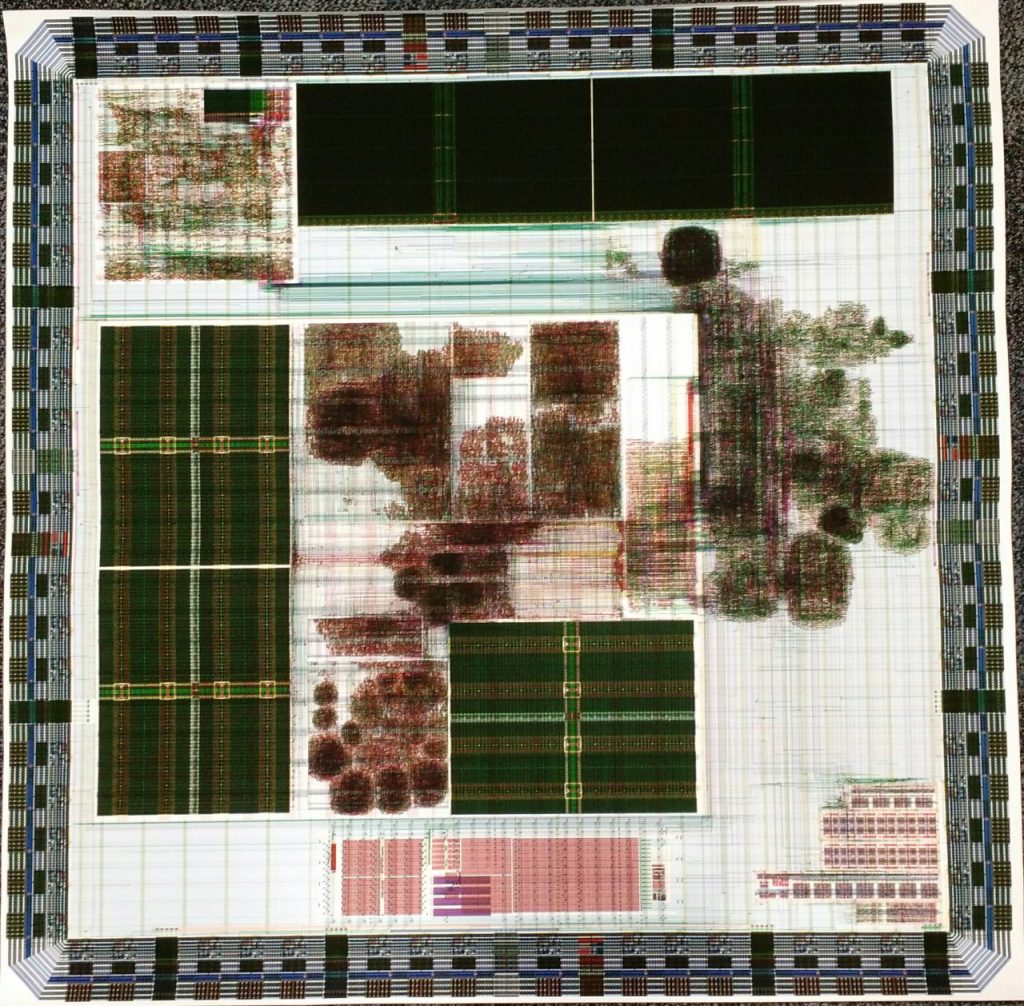

Tokachi-3A

This demonstrator, code-name “Tokachi-3A”, was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Tokachi-3A was taped out in March 2012, packaged and delivered in July 2012 and has supported evaluation of place-and-route strategies for IP watermarking. The Tokachi-3A technology demonstrator – TSMC65LP

Read Article +

Tokachi-1 and 2

Tokachi-1 and -2 technology demonstrators were taped out and manufactured in 2011 to showcase research into register state integrity and advanced power gating and state retention techniques that build on the capabilities that are now well supported by current EDA tools and implementation flows. Building on the multi-voltage tools enhancements the initial technology demonstrator, code-name “Tokachi-1”, was designed as a collaboration with Arm Ltd who provided microprocessor core technology and latest State-Retention Power-Gating (SRPG) power management kits to augment the Physical IP for the 65nm Low-Power process technology available from TSMC Inc. Tokachi-1 low power technology demonstrator, TSMC65LP The chip…

Read Article +

COILS-C1

COILS-C1, taped-out out in November 2018, is the latest in a series of test-chips investigating low-cost 3D die stacking using near-field wireless communication. This two-tier SoC, fabricated using a TSMC 65nm process, incorporates two Arm Cortex M0 CPU cores in…Read Article +

ICLexperimenter-2018

Taped-out in May 2018, ICL-Experimenter is the first in a series of Arm-ECS research centre test-chips designed to explore wireless 3D integration using inductive coupling links. The chip was fabricated in AMS 0.35um technology with two vertically stacked dies within…Read Article +

Pipistrelle-4

Pipistrelle-4, taped-out at the end of May 2017, is the latest in a series of low-energy sensor-system chips. The chip includes circuit/system ideas from multiple PhD research students and industry, focusing on an energy and performance optimised SRAM bitcell, low-area…Read Article +

ECStest-2016

Taped-out in October 2016 this test-chip was designed to explore on chip wireless communication in the mm-wave frequency band. The chip was fabricated in an AMS 0.35um technology and incorporates two meander monopole antennas (which can be observed in the…Read Article +

Pipistrelle-3

Taped out in March 2016, this chip advanced Pipistrelle-2’s design by adding forward body-bias to improve performance at low voltage as well as an autonomous dynamic voltage and frequency scaling (DVFS) control state machine for carefully sequencing clocks, regulator settings…Read Article +

Pipistrelle-2

This chip advances Pipistrelle-1’s design, taking another step towards filling in the pieces required to build an autonomous minimum-energy sensor system. Low power clock sources are an important part of a minimum energy system for driving CPUs, switched-capacitor converters, power-management…Read Article +

Pipistrelle-1

A sub-threshold demonstrator chip, incorporating innovative features for energy harvesting and power conversion, has been designed and taped-out by Arm R&D engineers and ECS researchers. Pipistrelle-1 Minimum energy systems are important for deployable multi-billion wireless sensor networks (WSNs). This sub-threshold…Read Article +

Cricket-1

This demonstrator, code-name “Cricket-1”, was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Cricket-1 was taped out in September 2013, arriving back from fab in January…Read Article +

Tokachi-4M

This low-power technology demonstrator, code-name “Tokachi-4M”, contains 16x Cortex-M0 CPU cores and was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Tokachi-4M was taped out in…Read Article +

Tokachi-4A

This advanced state-retention power-gating demonstrator, code-name “Tokachi-4A”, contains a Cortex-M0 system control processor and a dual-core Cortex-A5 application processor subsystem, again designed as a collaboration with Arm Ltd on TSMC 65nm Low-Power process technology available. Tokachi-4A was taped out in…Read Article +

Tokachi-3M

This demonstrator, code-name “Tokachi-3M”, was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Tokachi-3M was taped out in March 2012. Tokachi-3M IP watermarking demonstrator, TSMC65LPRead Article +

Tokachi-3A

This demonstrator, code-name “Tokachi-3A”, was designed as a collaboration with Arm Ltd with the Physical IP designed for the 65nm Low-Power process technology available from TSMC Inc. Tokachi-3A was taped out in March 2012, packaged and delivered in July 2012…Read Article +

Tokachi-1 and 2

Tokachi-1 and -2 technology demonstrators were taped out and manufactured in 2011 to showcase research into register state integrity and advanced power gating and state retention techniques that build on the capabilities that are now well supported by current EDA…Read Article +

Software Tools

Our software tools are released to the community so that others can benefit from our research findings and methodologies.

Fused: Full-System Simulation of Energy-Driven Computers

Fused is a full-system simulator for modelling energy-driven computers. To accurately model the interplay between energy-availability, power consumption, and execution; Fused models energy and execution in a closed feedback loop. The power model is based on recording high-level events (memory accesses, peripheral operations etc.) and states (modules on/off, peripheral operation modes etc.), and computing the instantaneous power consumption at runtime. Simultaneously, external circuitry such as e.g. energy storage, power supply and power management is modelled. The power consumption, power supply, and energy-availability, is then used to calculate the supply voltage, which in turn is monitored by the modeled microcontroller. In…

Read Article +

COIL-3D

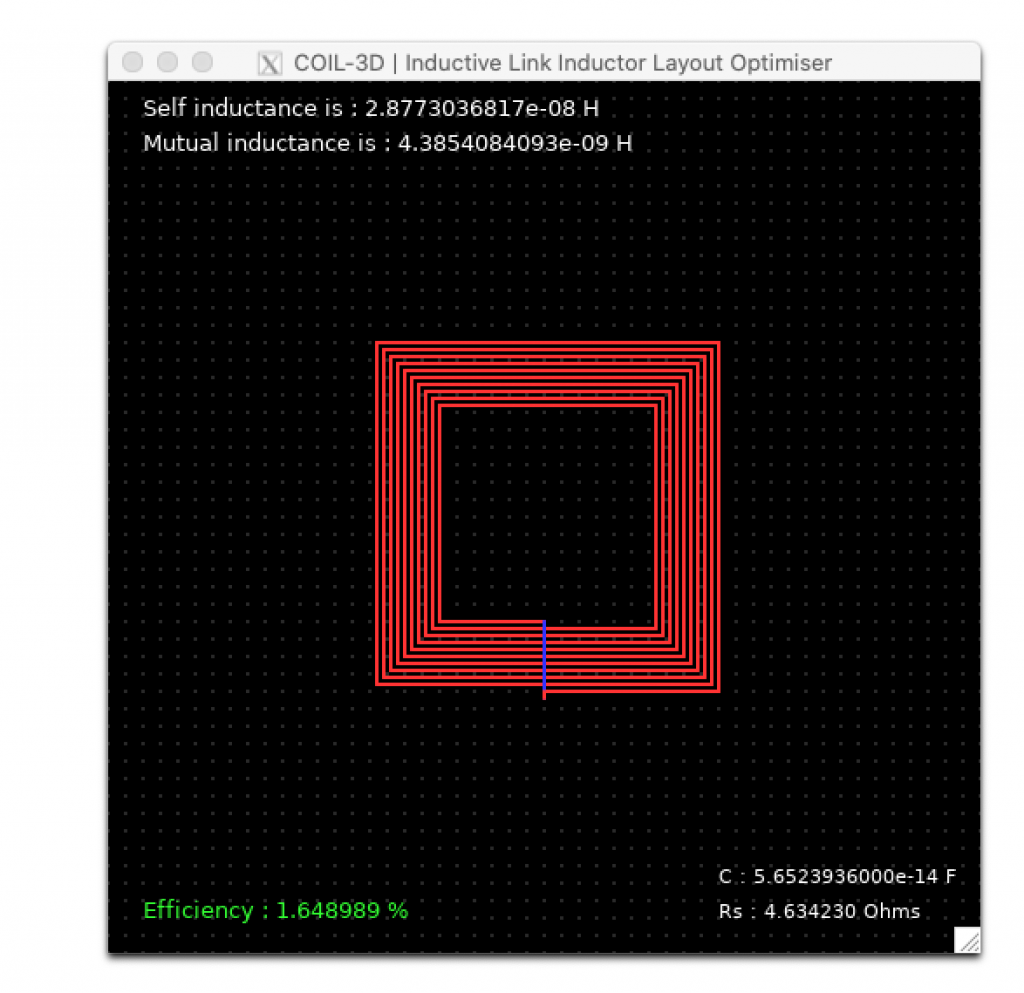

COIL-3D is a CAD tool for determining best performing inductor geometries for use in Inductive Coupling Link (ICL) based Three Dimensional Integrated Circuits (3D-ICs), developed at the University of Southampton, in collaboration with Arm Research. The tool takes as its inputs a configuration file (*.cfg) describing the physical and electrical parameters required for the design and then generates an inductor layout to maximise the performance of the inductive channel, for data transmission at a given frequency. COIL-3D consists of two main elements: The solver: a set of mathematical expressions to compute the electrical characteristics of the link directly from its…

Read Article +

GemStone: Hardware-Validated CPU Performance and Energy Modelling

GemStone is a suite of five software tools that, together, identify and evaluate the sources of error in gem5 models against a reference hardware (HW) platform by utilising statistical and machine learning approaches. Independently, the tools serve many purposes: Automating the running of experiments and collection of Performance Monitoring Counters (and temperature and power on supported platforms) on Arm-based devices (ARMv7 and ARMv8); Automating the running of gem5 simulations and aggregating the results; Applying Powmon power models to the hardware results; Applying Powmon power models to gem5 simulation data; Combining the HW and gem5 model characterisations and applying statistical and…

Read Article +

PowMon: Accurate and Stable CPU Power Estimation

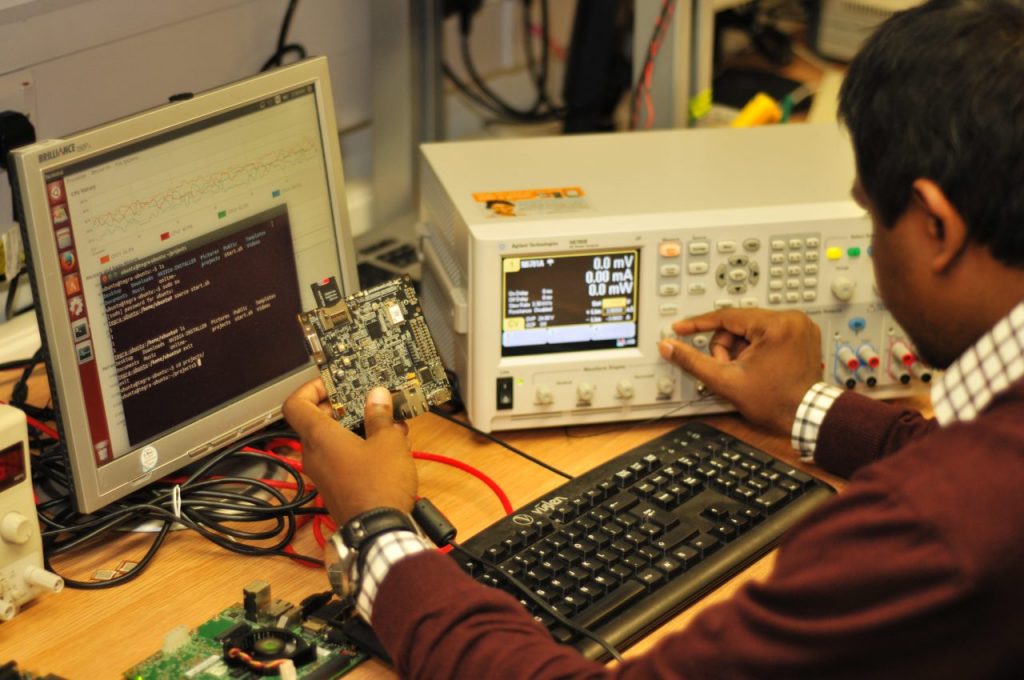

Being able to accurately estimate CPU power consumption is a key requirement for both controlling online CPU energy-saving techniques and design-space exploration. Models built and validated using measured data from an actual device are extremely valuable as their accuracy is known and trusted. PowMon produces power models that are both accurate and stable. The open source PowMon software tools consists of a number of distinct parts: Software tools which allow researchers to implement our automated model building methodology, and produce power models of a platform that are both accurate and stable. Downloadable power models for existing mobile CPUs (quad-core Cortex-A7 and quad-core…

Read Article +

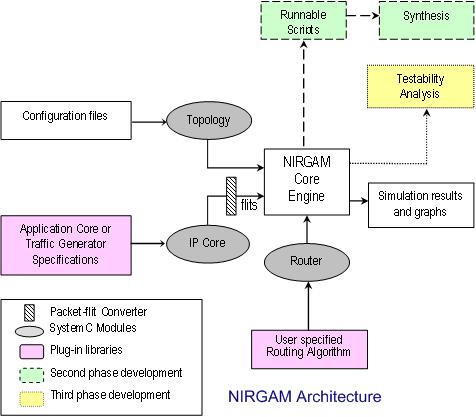

NIRGAM: A Simulator for NoC Interconnect Routing and Application Modeling

NIRGAM is a systemC based discrete event, cycle accurate simulator for research in Network on Chip(NoC). It provides substantial support to experiment with NoC design in terms of routing algorithms and applications on various topologies.

Read Article +

Fused: Full-System Simulation of Energy-Driven Computers

Fused is a full-system simulator for modelling energy-driven computers. To accurately model the interplay between energy-availability, power consumption, and execution; Fused models energy and execution in a closed feedback loop. The power model is based on recording high-level events (memory…Read Article +

COIL-3D

COIL-3D is a CAD tool for determining best performing inductor geometries for use in Inductive Coupling Link (ICL) based Three Dimensional Integrated Circuits (3D-ICs), developed at the University of Southampton, in collaboration with Arm Research. The tool takes as its…Read Article +

GemStone: Hardware-Validated CPU Performance and Energy Modelling

GemStone is a suite of five software tools that, together, identify and evaluate the sources of error in gem5 models against a reference hardware (HW) platform by utilising statistical and machine learning approaches. Independently, the tools serve many purposes: Automating…Read Article +

PowMon: Accurate and Stable CPU Power Estimation

Being able to accurately estimate CPU power consumption is a key requirement for both controlling online CPU energy-saving techniques and design-space exploration. Models built and validated using measured data from an actual device are extremely valuable as their accuracy is…Read Article +