ICLexperimenter-2018

ICL Experimenter 2018

Taped-out in May 2018, ICL-Experimenter is the first in a series of Arm-ECS research centre test-chips designed to explore wireless 3D integration using inductive coupling links. The chip was fabricated in AMS 0.35um technology with two vertically stacked dies within each IC. This initial prototype contains eight wireless channels, each of which communicates over a distance of 120um (through 100um of silicon substrate + 20um of epoxy adhesive) and focusses on exploring different transceiver designs and inductor layouts.

Wireless 3D integration is a novel approach to 3D die stacking which avoids the inflated design, fabrication and manufacturing costs associated with using through silicon vias (TSVs). In such wirelessly stacked 3D systems, transmit data is encoded as a series of current pulses which are driven through a planar metal inductor fabricated in the upper interconnect layers of the transmitting die. As these current pulses flow through the inductor, an electromagnetic field is formed within the 3D stack which can be sensed by similar planar inductors in neighbouring dies (through electromagnetic induction), and hence used to recover the transmitted data stream.

Whilst wireless 3D integration provides several cost benefits when compared with the use of TSV-based 3D integration, it is often criticised for its reduced power efficiency. At the Arm-ECS research centre, we have recently been working to address this challenge. As part of this test-chip, we have designed a super-low energy transceiver, that uses time-domain data encoding to reduce the power consumption of such ICs, which has recently been accepted for publication at the prestigious European solid-state circuits conference (ESSCIRC) later this year.

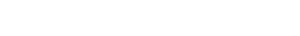

The test chip highlighting the proposed low-energy transceiver

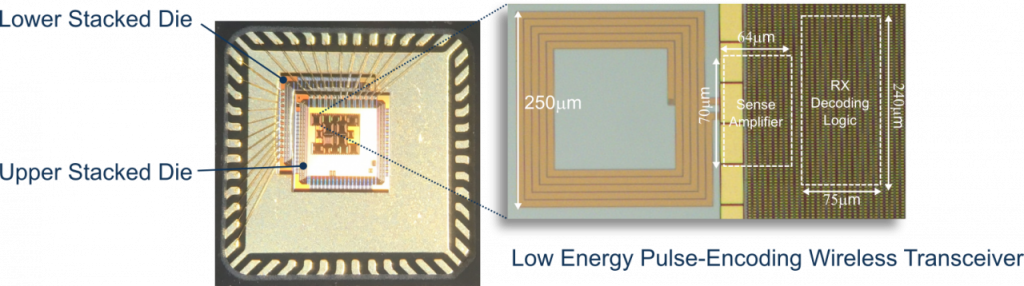

The figure above shows the test chip, highlighting the proposed low-energy transceiver. By combining: (1) 3-ary pulse-position modulation, to encode data in terms of the latency between sequential pulses (rather than using one-to-one pulse code mappings), and (2) A tunable current driver circuit to adjust the transmit current dynamically based on the quality of the stacked die assembly, the test chip outperforms existing transceivers by 5.3x in terms of energy-per bit/micron-channel-length as shown in the figure below.

Energy-per bit/micron-channel-length

Related Projects

Related People

Related Publications

-

Benjamin James Fletcher, Shidhartha Das and Terrence Mak “A spike-latency transceiver with tuneable pulse control for low-energy wireless 3D integration”. IEEE Journal of Solid State Circuits, 2020. (doi:10.1109/JSSC.2020.2989543)May 2020

-

Benjamin Fletcher, Shidhartha Das, and Terrence Mak, (2019) A 10.8pJ/bit pulse-position inductive transceiver for low-energy wireless 3D integration. In IEEE European Solid-State Circuits Conference (ESSCIRC). vol. 49, IEEE. 4 pp.Aug 2019

Related News

Outstanding Arm-ECS graduate claims Young Engineer of the Year accolade

Paper accepted in IEEE Journal of Solid State Circuits

6th May 2020

Read Article +

Lego-style wireless silicon stacking awarded parliament prize

19th March 2020

Read Article +

Making Stacking Silicon as Easy as Stacking Lego (2/2)

11th November 2019

Read Article +

ICL Experimenter Test Chip Taped Out

31st May 2018

Read Article +

Related Theses

-

Fletcher, Ben (2020) Cost-Effective 3D-IC Design using Near-Field Inter-Tier Wireless Communication. University of Southampton, Electronics and Computer Science, Doctoral Thesis.Sep 2020