Pipistrelle-3

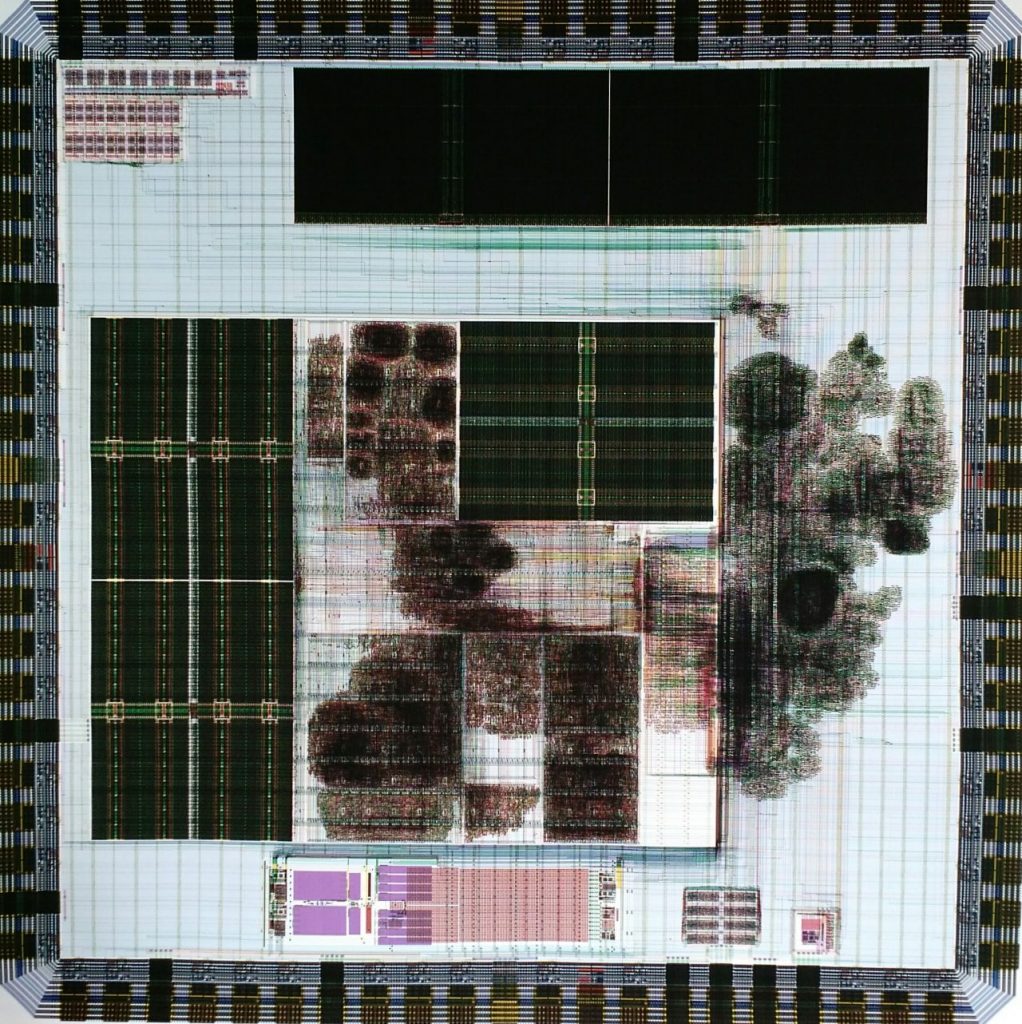

Pipistrelle-3 Test Chip

Taped out in March 2016, this chip advanced Pipistrelle-2’s design by adding forward body-bias to improve performance at low voltage as well as an autonomous dynamic voltage and frequency scaling (DVFS) control state machine for carefully sequencing clocks, regulator settings and body-bias. Additional integration of the switched-capacitor regulator and harvester has been made possible by adding numerous low–power oscillators along with further efficiency improvement and a reverse current protection scheme.

A fully integrated voltage monitor assists with rapid DVFS transitions between super/near/sub-threshold operating modes, while consuming only 50nW – this work was presented at VLSI-D 2017. Further, building on oscillator work from Pipistrelle-2, this chip demonstrates the first <nW/kHz RC oscillator and shows high temperature and voltage stability – this work was presented at ISSCC 2017.

Pipistrelle-3 Test Chip